Additionally, the algorithms for Vivado are implemented with having the ever-growing size of FPGAs in mind.

That for instance allows you to trace back a signal that the post-place-and-route-static-timing-report identifies as your critical path, back to your HDL code.

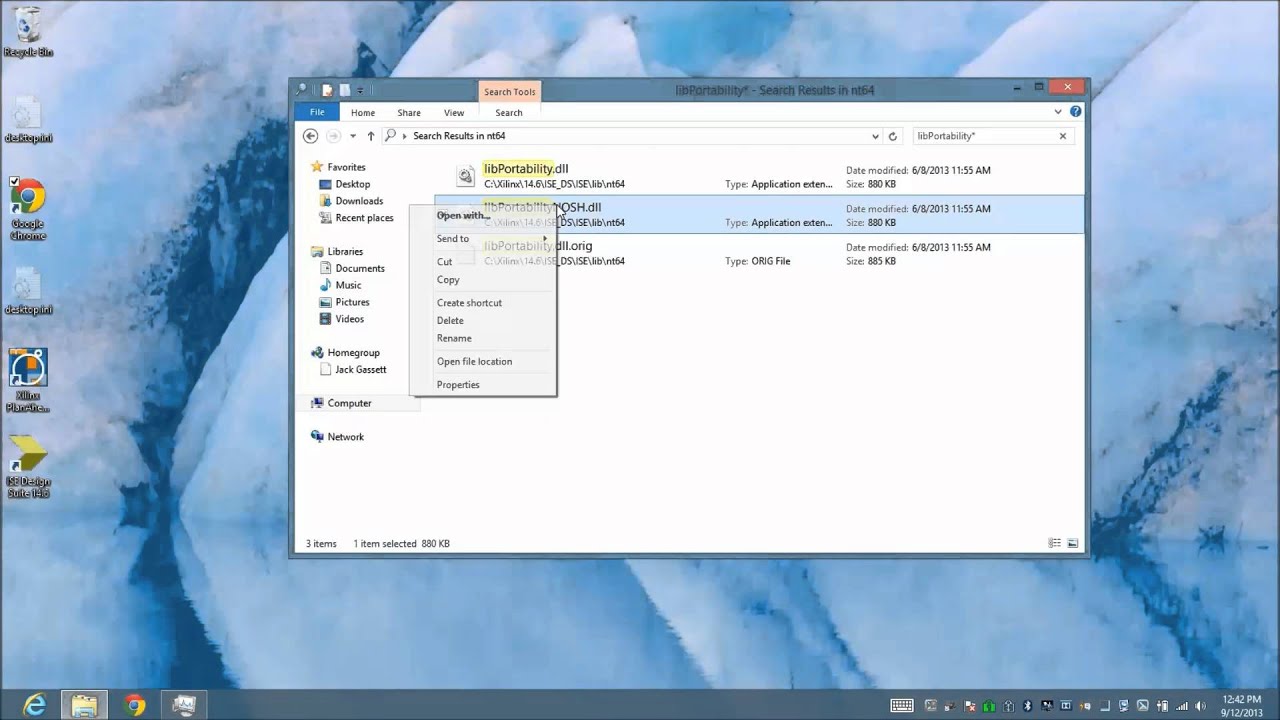

In Vivado, all steps have the same view on a global data structure. For instance, in ISE, each 'step' was actually a different binary tool that communicated via files with each other and ISE was actually mainly a GUI to connect them. Xilinx told me at a booth that they completely re-developed Vivado from scratch (starting about 5 years before it was released) with new algorithms for all steps (place and route, etc.) and new data bases for internal management.

0 kommentar(er)

0 kommentar(er)